The highest value required for the Pearson's Correlation Coefficient (an intermediate value in the calculation) is

Nmax2 * Xmax x Ymax, or 11 * 11 * 126 * 126 = 1,920,996.

That fits into 21 bits (221=2,097,152).

By doing an 8-bit left shift prior to division, now requiring 29-bit registers, I can let Verilog just truncate the fractional part.

Using one byte for the correlation coefficient, b.bbbbbb, is enough to represent a value down to +/- 2-7, or +/-0.0078125.

There is probably no reason to make pearsons_r out of 29-bit registers, so they'll be 32-bit wide.

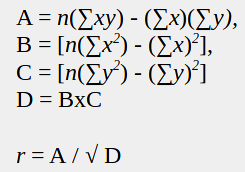

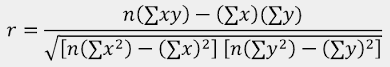

The calculation can be broken down into the form: