| oneproc level tests |

| [ ] VID_OP_func_assert_abortDeassertBeforeIdle_ERR | oneproc_abort_test | - |

| [ ] VID_OP_func_assert_readB4OKandReady_ERR | oneproc_badProtocol_1_test | - |

| [ ] VID_OP_func_assert_readReqWithdrawnAfterReadyToRead_ERR | oneproc_badProtocol_1_test | - |

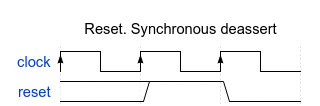

| [ ] VID_OP_func_assert_resetDeassertNotSynchronous_ERR | oneproc_badProtocol_1_test | - |

| [ ] VID_OP_func_assert_loadToAvailableDeassertDelay_ERR | oneproc_badProtocol_1_test | - |

| [ ] VID_OP_func_assert_thanksToAvailableAssertDelay_ERR | oneproc_badProtocol_1_test | - |

| [ ] VID_OP_func_assert_thanksToAvailableDeassertDelay_ERR | oneproc_badProtocol_1_test | - |

| [D] VID_OP_func_assert_writeB4available_ERR | oneproc_badProtocol_1_test | - |

| [ ] VID_OP_func_assert_writeB4OKandReady_ERR | oneproc_badProtocol_1_test | - |

| [D] VID_OP_func_assert_writeWithoutLoad_AvailableDoesNotDeassert | - |

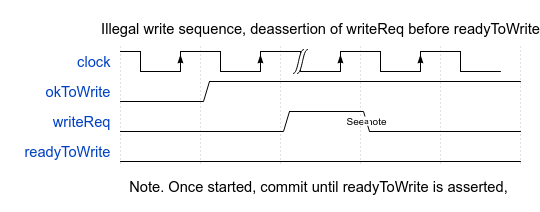

| [D] VID_OP_func_assert_writeReqWithdrawnAfterReadyToWrite_ERR | oneproc_badProtocol_1_test | - |

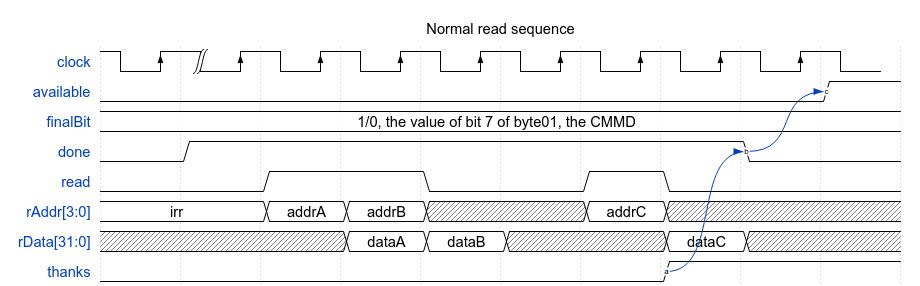

| [ ] VID_OP_func_assert_thanksOnNullRead | oneproc_SMOOTH_1_pipeline_final_test | - |

|

| [ ] VID_OP_func_assert_assertRunAfterLoad | oneproc_SMOOTH_0_pipeline_test

oneproc_SMOOTH_1_pipeline_test

oneproc_SMOOTH_1_pipeline_final_test | - |

| [ ] VID_OP_func_assert_assertRunAfterLoad | oneproc_SMOOTH_0_pipeline_test

oneproc_SMOOTH_1_pipeline_test

oneproc_SMOOTH_1_pipeline_final_test | - |

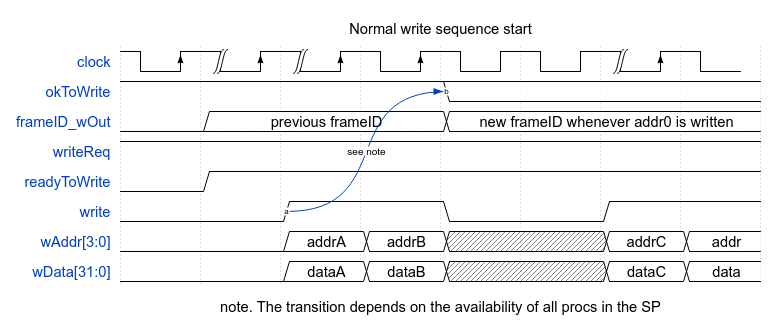

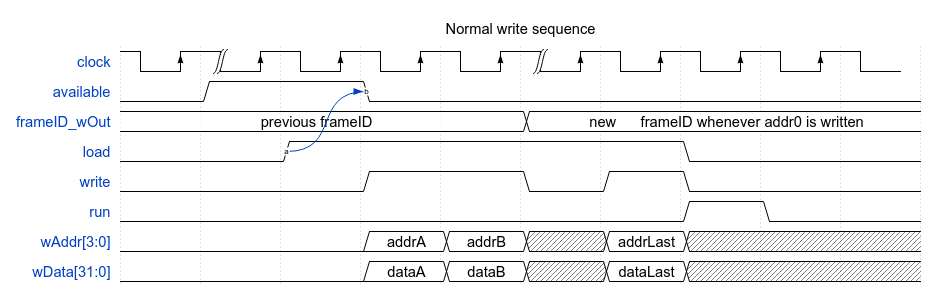

| [*] [ ] VID_OP_func_assert_frameID_wOutExported | oneproc_CMMD_mix_1_test | oneproc_if |

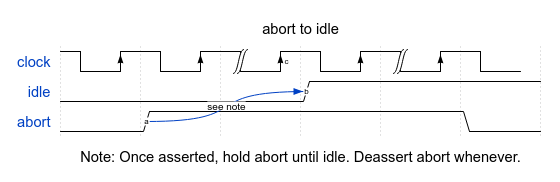

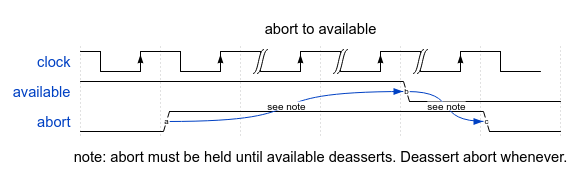

| [ ] VID_OP_func_assert_normalAbort | oneproc_abort_test | - |

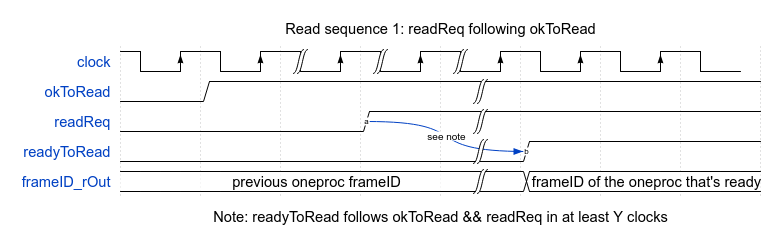

| [ ] VID_OP_func_assert_readReqAfterOkToRead | oneproc_ProtocolVariations_1_test | - |

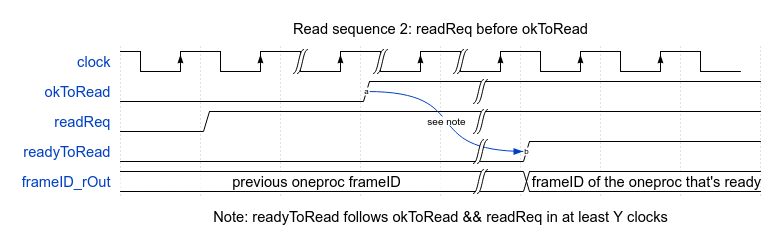

| [ ] VID_OP_func_assert_readReqB4okToRead | oneproc_ProtocolVariations_1_test | - |

| [ ] VID_OP_func_assert_frameID_rOutFollows | oneproc_CMMD_mix_1_test | - |

| [*] VID_OP_func_assert_finalBitFollows | oneproc_SMOOTH_1_pipeline_final_test | - |

| [ ] VID_OP_func_assert_readReqBeforeOkToRead | oneproc_ProtocolVariations_1_test | - |

| [ ] VID_OP_func_assert_readReqWithdrawnOK | oneproc_ProtocolVariations_1_test | - |

| [ ] VID_OP_func_assert_loadWritesInParts | oneproc_ProtocolVariations_1_test | - |

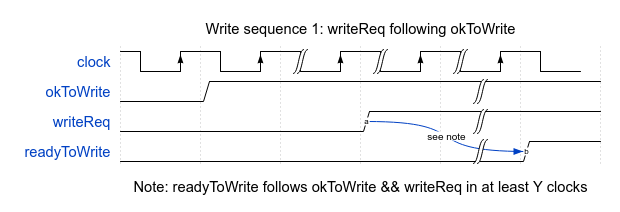

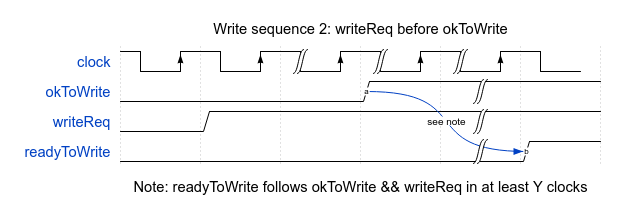

| [ ] VID_OP_func_assert_writeReqB4okToWrite | oneproc_ProtocolVariations_1_test | - |

| [ ] VID_OP_func_assert_loadWithoutWrite | oneproc_ProtocolVariations_1_test | - |

| [ ] VID_OP_func_assert_availableDeassertOnWrite | oneproc_ProtocolVariations_1_test | - |

[D] VID_OP_func_assert_writeBeforeAvailable_ERR<- |

|

[*] VID_OP_func_self_pipeline

[*] VID_OP_func_self_pipeline_nullWithFinal

[ ] VID_OP_func_self_pipeline_ChangeCMMD | oneproc_SMOOTH_0_pipeline_test

oneproc_SMOOTH_1_pipeline_test

oneproc_SMOOTH_1_pipeline_final_test | - |

|

| [ ] VID_OP_func_assert_readyToWriteLeadsWriteReq_ERR | oneproc_ProtocolVariations_1_test | - |

| [ ] VID_OP_func_assert_readyToReadLeadsReadReq_ERR | oneproc_ProtocolVariations_1_test | - |

|

| [ ] VID_OP_rand_assert_cprop_abortWithinYYY | placeholdernameoftest | - |

| [ ] VID_OP_rand_assert_CMMDtoAvailableInMclocks | placeholdernameoftest | - |

| [D] VID_OP_rand_assert_sillyRead | placeholdernameoftest | - |

|

| [ ] VID_OP_rand_ccover_assert_abortToavailableTime | placeholdernameoftest | - |

|

| [ ] VID_OP_func_cover_abort | oneproc_abort_test | - |

| [ ] VID_OP_func_self_CORRearlyDoneOnArg1match | oneproc_CORR_1_single_test | - |

| [ ] VID_OP_func_self_CORRmatch | oneproc_CORR_0_single_test

oneproc_CORR_1_single_test | - |

| [ ] VID_OP_func_self_NOPdoesNotChangeDataRecord | oneproc_NOP_test | - |

| [ ] VID_OP_func_self_BadCMMD | oneproc_BADCMMD_test | - |

| [D] VID_OP_func_self_writeWithoutLoad | - |

| [D] VID_OP_func_self_writeWithoutLoad_ERR | - |

| [D] VID_OP_func_self_loadWritesInParts | - |

| [D] VID_OP_func_self_loadWithoutWrite | - |

| [ ] VID_OP_rand_self_pipeline | placeholdernameoftest | - |

| HWSP level tests |

| [l] VID_SP_func_assert_abortDeassertBeforeIdle_ERR | placeholdernameoftest |

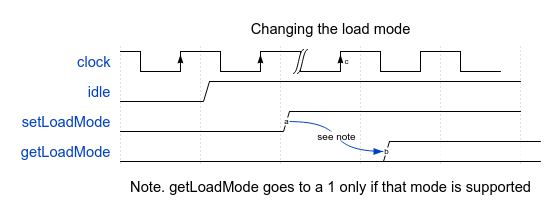

| [l] VID_SP_func_assert_getLoadModeIsSet_ERR | placeholdernameoftest |

| [D] VID_SP_func_assert_readB4OKandReady_ERR | placeholdernameoftest |

| [D] VID_SP_func_assert_readReqWithdrawnAfterReadyToRead_ERR | placeholdernameoftest |

| [l] VID_SP_func_assert_readyToReadMoreThanYclocks_ERR | placeholdernameoftest |

| [l] VID_SP_func_assert_readyToWriteMoreThanXclocks_ERR | placeholdernameoftest |

| [l] VID_SP_func_assert_resetDeassertNotSynchronous_ERR | placeholdernameoftest |

| [l] VID_SP_func_assert_setLoadModeNotIdle_ERR | placeholdernameoftest |

| [D] VID_SP_func_assert_writeReqWithdrawnAfterReadyToWrite_ERR | placeholdernameoftest |

|

| [l] VID_SP_func_assert_frameID_wOutFollows | placeholdernameoftest |

| [l] VID_SP_func_assert_idleFollowsAbort | placeholdernameoftest |

| [l] VID_SP_func_assert_idleFollowsAllProcsDone | placeholdernameoftest |

| [l] VID_SP_func_assert_normalAbort | placeholdernameoftest |

| [D] VID_SP_func_assert_readReqAfterOkToRead | placeholdernameoftest |

| [D] VID_SP_func_assert_readReqB4okToRead | placeholdernameoftest |

| [D] VID_SP_func_assert_readReqBeforeOkToRead | placeholdernameoftest |

| [l] VID_SP_func_assert_frameID_rOutFollows | placeholdernameoftest |

| [l] VID_SP_func_assert_finalBitFollows | placeholdernameoftest |

| [D] VID_SP_func_assert_readReqWithdrawnOK | placeholdernameoftest |

| [l] VID_SP_func_assert_setLoadModeParallelAttempted | placeholdernameoftest |

| [l] VID_SP_func_assert_setLoadModeSerialAttempted | placeholdernameoftest |

| [D] VID_SP_func_assert_writeReqAfterOkToWrite | placeholdernameoftest |

| [D] VID_SP_func_assert_writeReqB4okToWrite | placeholdernameoftest |

| [D] VID_SP_func_assert_writeReqBeforeOkToWrite | placeholdernameoftest |

| [D] VID_SP_func_assert_writeReqWithdrawnOK | placeholdernameoftest |

| [D] VID_SP_func_assert_writeB4OKandReady_ERR |

|

| [l] VID_SP_func_self_OoOcompletes | placeholdernameoftest |

| [l] VID_SP_func_self_pipeline | placeholdernameoftest |

|

| [l] VID_SP_rand_assert_frameID_wOutMismatch_ERR | placeholdernameoftest |

| [D] VID_SP_func_assert_readyToReadLeadsReadReq_ERR | placeholdernameoftest |

| [D] VID_SP_func_assert_readyToWriteLeadsWriteReq_ERR | placeholdernameoftest |

|

| [l] VID_SP_rand_assert_cprop_abortWithinXYZ | placeholdernameoftest |

| [l] VID_SP_rand_assert_FillAndKeepFull | placeholdernameoftest |

| [l] VID_SP_rand_assert_FillThenDrain | placeholdernameoftest |

| [D] VID_SP_rand_assert_sillyRead | placeholdernameoftest |

| [l] VID_SP_rand_assert_SingleComputation | placeholdernameoftest |

|

| [l] VID_SP_rand_self_CMMDarg0onlyChange | placeholdernameoftest |

| [l] VID_SP_rand_cover_abort | placeholdernameoftest |

| [l] VID_SP_rand_self_OoOcompletes | placeholdernameoftest |

| [l] VID_SP_rand_self_pipeline | placeholdernameoftest |

Current tests: