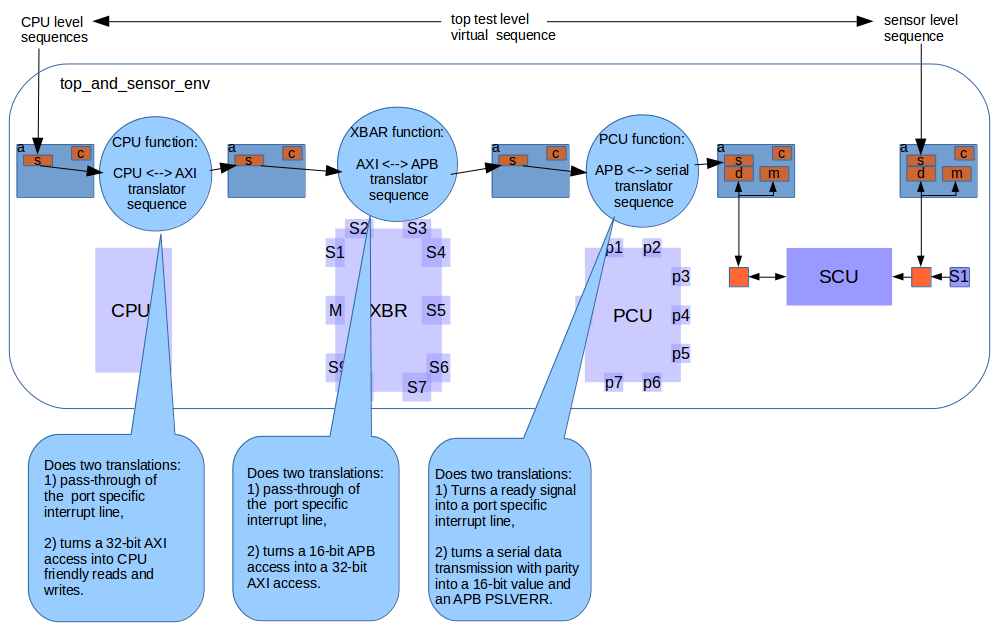

virtual task body(); The blue color represents the upstream activity, the PCU.

The green color represents the downstream activity, the SCU.

PCU_txn p_txn;

SCU_txn s_txn;

forever begin

pcu_token.get(1) ;

pcu_sequencer.get_next_item(p_txn);

s_txn = SCU_txn::type_id::create(.name("s_txn"), .contxt(get_full_name()));

start_item(s_txn);

s_txn.go = ~p_txn.PWRITE ;

finish_item(s_txn);

p_txn.PRDATA = {7'b0,s_txn.txdata} ;

parity = ((s_txn.txdata[0] ^ s_txn.txdata[1]) ^

(s_txn.txdata[2] ^ s_txn.txdata[3]) ^

(s_txn.txdata[4] ^ s_txn.txdata[5]) ^

(s_txn.txdata[6] ^ s_txn.txdata[7])) ;

p_txn.PSLVERR = ( parity != s_txn.parity) ? 1 : 0 ;

`uvm_info("PCU_SCU_xlator_data_seq", $sformatf("PRDATA = %h", p_txn.PRDATA), UVM_MEDIUM)

`uvm_info("PCU_SCU_xlator_data_seq", $sformatf("PSLVERR = %h", p_txn.PSLVERR), UVM_MEDIUM)

pcu_sequencer.item_done ;

pcu_token.put(1) ;

end

endtask: body

|